## UM10025\_2

## ISP110x Eval Kit User Manual for the HVQFN14/16 Package Rev. 02.00 — 12 April 2004

User manual

#### Document information

| Info     | Content                                                               |

|----------|-----------------------------------------------------------------------|

| Keywords | ISP1102, ISP1104, ISP1105, ISP1106, USB, universal serial bus,        |

|          | transceiver                                                           |

| Abstract | The ISP110x eval board helps you to evaluate the features of the      |

|          | ISP110x. This document explains the evaluation of the ISP110x for the |

|          | HVQFN14 and HVQFN16 packages.                                         |

|          | Notes: ISP110x denotes the ISP1102, ISP1104, ISP1105 and ISP1106      |

|          | Philips Advanced Universal Serial Bus transceivers, and any future    |

|          | derivatives.                                                          |

#### Revision history

| Rev | Date     | Description     |

|-----|----------|-----------------|

| 2.0 | Mar 2004 | Removed ISP1107 |

| 1.0 | May 2003 | First release   |

#### Contact information

For additional information, please visit: http://www.semiconductors.philips.com/

For sales office addresses, please send an email to: sales.addresses@www.semiconductors.philips.com

### DISCLAIMER

PRODUCT IS DEEMED ACCEPTED BY RECIPIENT. THE PRODUCT IS PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, PHILIPS SEMICONDUCTORS FURTHER DISCLAIMS ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANT ABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NONINFRINGEMENT. THE ENTIRE RISK ARISING OUT OF THE USE OR PERFORMANCE OF THE PRODUCT AND DOCUMENTATION REMAINS WITH THE RECIPIENT. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, IN NO EVENT SHALL PHILIPS SEMICONDUCTORS OR ITS SUPPLIERS BE LIABLE FOR ANY CONSEQUENTIAL, INCIDENTAL, DIRECT, INDIRECT, SPECIAL, PUNITIVE, OR OTHER DAMAGES WHATSOEVER (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF BUSINESS PROFITS, BUSINESS INTERRUPTION, LOSS OF BUSINESS INFORMATION, OR OTHER PECUNIARY LOSS) ARISING OUT OF THIS AGREEMENT OR THE USE OF OR INABILITY TO USE THE PRODUCT, EVEN IF PHILIPS SEMICONDUCTORS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **Contents**

| ١. | ISP1 | 10X EVAL BOARD                                           | 5  |

|----|------|----------------------------------------------------------|----|

|    |      | Objective                                                |    |

|    | 1.2. | Description                                              |    |

| 2. | МО   | DE SELECTION FOR APPLICATIONS                            | 7  |

| 3. | PO\  | NER SUPPLY CONFIGURATIONS                                | 8  |

| 1. | FUN  | ICTION TESTING                                           | 9  |

|    | 4.1. | Function Selection                                       | 9  |

|    | 4.2. | Driver Interface Selection for ISP1104; ISP1105; ISP1106 | 9  |

|    | 4.3. | Driver Interface Selection for the ISP1102               | 10 |

| 5. | SCH  | IEMATIC OF THE ISP110X HVQFN14 AND HVQFN16 PACKAGES      | 11 |

| ó. | BILL | OF MATERIALS FOR THE ISP110X EVAL BOARD                  | 13 |

| 7. | REF  | erences                                                  | 13 |

The names of actual companies and products mentioned herein may be the trademarks of their respective owners. All other names, products, and trademarks are the property of their respective owners.

*Note*: ISP110x denotes the ISP1102, ISP1104, ISP1105, and ISP1106 Philips Advanced Universal Serial Bus transceivers, and any future derivatives.

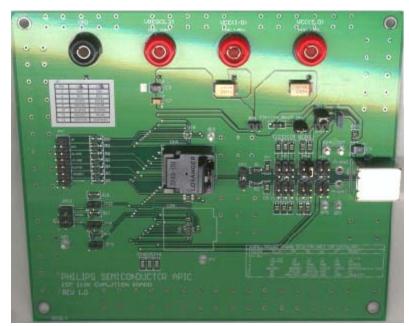

#### 1. ISP110x Eval Board

#### 1.1. Objective

The ISP110x evaluation (eval) board helps you to evaluate the features of the ISP110x.

This document explains the evaluation of the ISP110x for the HVQFN14 and HVQFN16 packages, which are cheaper than the HBCC16 package.

#### 1.2. Description

The ISP110x is a generic Universal Serial Bus (USB) transceiver integrated circuit (IC) that is compliant with *Universal Serial Bus Specification Rev. 2.0.* It operates linearly from 3.3 V to 5.0 V, and is backward compatible with Philips' PDIUSBP11A.

Both the PDIUSBP11A and the ISP110x support two types of driver interfaces: the Philips encoded data interface and the USB-IF standard data interface. This compatibility allows greater flexibility in designs and applications.

To facilitate testing, all the ISP110x pins are connected to one side of the JP7 and JP12 headers. The other side is connected to the ground. Some ISP110x pins, such as MODE,  $\overline{\text{OE}}$ , SUSPND, VMO/FSE0, VPO/VO, SOFTCON and SPEED, are pulled up using 1 M $\Omega$  resistors.

Jumper settings can be used to configure transceivers and capacitors for characterization functions.

The mode of operating the eval board depends on the IC used, as well as some jumpers' settings for signaling requirement.

Figure 1-1: ISP110x Eval Kit for the HVQFN14 and HVQFN16 Packages

Table 1-1 shows the signal contents of headers and their corresponding signal names in the ISP110x.

Table 1-1: Signal Contents of Headers and their Corresponding Signal Names in the ISP110x

| Header | Signal                   |                        | In              |                        |                        |  |  |

|--------|--------------------------|------------------------|-----------------|------------------------|------------------------|--|--|

|        |                          | ISP1102                | ISP1104         | ISP1105                | ISP1106                |  |  |

| JP7    | $\overline{\mathrm{OE}}$ | $\overline{\text{OE}}$ | $\overline{OE}$ | $\overline{\text{OE}}$ | $\overline{\text{OE}}$ |  |  |

|        | RCV                      | RCV                    | RCV             | RCV                    | RCV                    |  |  |

|        | VP                       | VP/VPO                 | VP              | VP                     | VP                     |  |  |

|        | VM                       | VM/VMO                 | VM              | VM                     | VM                     |  |  |

|        | SUSPEND                  | SUSPEND                | SUSPEND         | SUSPEND                | SUSPEND                |  |  |

|        | SPEED                    | VBUSDET                | VBUSDET         | SPEED                  | SPEED                  |  |  |

|        | SOFTCON                  | SOFTCON                | SOFTCON         | SOFTCON                | SOFTCON                |  |  |

| JP12   | Pin 6                    | No connection          | MODE            | MODE                   | GND                    |  |  |

|        | Pin 12                   | No connection          | VMO/FSE0        | VMO/FSE0               | VMO                    |  |  |

|        | Pin 11                   | No connection          | VPO/VO          | VPO/VO                 | VPO                    |  |  |

Table 1-2 shows the jumper settings on the eval board.

| Jumper | Setting                                                   |

|--------|-----------------------------------------------------------|

| JP1    | Sharing mode or pull-down to GND on D+                    |

| JP2    | Sharing mode or pull-down to GND on D-                    |

| JP3    | Different capacitor leads for characterized testing on D+ |

| JP4    | Different capacitor leads for characterized testing on D- |

| JP5    | 1.5 k $\Omega$ pull-up or 15 k $\Omega$ pull-down on D-   |

| JP6    | 1.5 k $\Omega$ pull-up or 15 k $\Omega$ pull-down on D+   |

| JP8    | Short $V_{CC(5,0)}$ to $V_{reg(3,3)}$                     |

| JP9    | Connect to the V <sub>BUS</sub> line                      |

| JP10   | For back drive voltage purpose                            |

| JP11   | Connect to V <sub>pu(3.3)</sub>                           |

| JP13   | Connect to HVQFN16 pin 6                                  |

| JP14   | Connect to HVQFN16 pin 12                                 |

| JP15   | Connect to HVQFN16 pin 11                                 |

### 2. Mode Selection for Applications

Table 2-1: Mode Selection for the HVQFN16 Package

| IC Products and Packages | Connection                         | Operation Mode                                             |

|--------------------------|------------------------------------|------------------------------------------------------------|

| ISP1102                  | No connection                      | Differential Input Mode (VO/VPO, VM/VMO)—<br>Bidirectional |

| ISP1104                  | Short JP12 <sup>[1]</sup> and JP13 | Single-Ended Input Mode (VO, FSE0)                         |

|                          | Short JP13                         | Differential Input Mode (VPO, VMO)                         |

| ISP1105                  | Short JP12 <sup>[1]</sup> and JP13 | Single-Ended Input Mode (VO, FSE0)                         |

|                          | Short JP13                         | Differential Input Mode (VPO, VMO)                         |

| ISP1106                  | Short JP12 <sup>[1]</sup> and JP13 | Differential Input Mode (VPO, VMO)                         |

<sup>[1]</sup> Use jumper on pins 1 and 2.

#### 3. Power Supply Configurations

The ISP110x can be used with different power supply configurations by setting jumpers JP1, JP2, JP3 and JP4. These jumpers are used to suit the power supply application environment, as shown in Table 3-1.

Table 3-1: Power Supply Configurations

| Mode    | Environment                                   | Connected Voltages                          | Jumpers<br>Required | Remarks                                                                                                                                                                                                            |

|---------|-----------------------------------------------|---------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal  | +5.0 V operation (self-powered)               | $V_{\text{CC(5.0)}}$                        | Not<br>applicable   | Connect $V_{CC(5.0)}$ to a 5 V source (4.0 V to 5.5 V)                                                                                                                                                             |

|         |                                               | © CC(I/O)                                   |                     | Connect $V_{\text{cc(VO)}}$ to 1.65 V to 3.6 V range of the backend logic circuit (or external supply voltage)                                                                                                     |

|         | Bus-powered operation (V <sub>BUS</sub> line) | V <sub>BUS</sub> line                       | JP9                 | Connect to the V <sub>BUS</sub> line ( <i>Note</i> : Does not need any external source.)                                                                                                                           |

|         | +3.3 V operation (bypass mode)                | $V_{\text{CC(5.0)}}$ $V_{\text{reg(3.3V)}}$ | JP8                 | $V_{\text{\tiny CC(5.0)}}$ and $V_{\text{\tiny reg(3.3V)}}$ are shorted and connected to a 3.3 V source                                                                                                            |

|         |                                               | $V_{\text{CC(I/O)}}$                        |                     | Connect V <sub>cc(VO)</sub> to 1.65 V to 3.6 V range of the backend logic circuit (external supply voltage)                                                                                                        |

| Disable | +5.0 V operation (self-powered)               | V <sub>CC(5.0)</sub>                        | Not<br>applicable   | Connect V <sub>cc(6.0)</sub> to a 5 V source (4.0 V to 5.5 V) ( <i>Note</i> : No V <sub>cc(VO)</sub> is connected to the source.)                                                                                  |

| Sharing |                                               | $V_{\text{cc(I/O)}}$                        | Not<br>applicable   | Connect only V <sub>CC(I/O)</sub> to 1.65 V to 3.6 V range of the backend logic circuit (external supply voltage) ( <i>Note</i> : V <sub>CC(S,0)</sub> and V <sub>reg(3.3V)</sub> are not connected to the source) |

The ISP1102, ISP1105, and ISP1106 transceivers have a regulator bypass mode, in which  $V_{\text{cc}(5.0)}$  can be connected to  $V_{\text{reg}(3.3)}$  with a maximum voltage drop of 0.3 V (2.7 V to 3.6 V). The ISP1104 transceiver does not support this mode.

The ISP1102 and ISP1104 transceivers do not support the disable mode.

In the default setting (the normal bus-powered mode configuration), there are jumpers—JP9, JP11 and JP6—on pins 3 and 4.

#### 4. Function Testing

#### 4.1. Function Selection

Table 4-1: Function Table [1]

| SUSPND | <del>OE</del> | RCV                     | VP/VM  | D+ and D-    | Remarks                              |

|--------|---------------|-------------------------|--------|--------------|--------------------------------------|

| LOW    | LOW           | Active                  | Active | Active       | Driving and receiving (differential  |

|        |               |                         |        |              | receiver active)                     |

| HIGH   | LOW           | Inactive <sup>[2]</sup> | Active | Active       | Driving during suspend (differential |

|        |               |                         |        |              | receiver inactive)[3]                |

| LOW    | HIGH          | Active                  | Active | Hi-Z         | Receiving only <sup>[4]</sup>        |

| HIGH   | HIGH          | Inactive <sup>[2]</sup> | Active | $Hi-Z^{[4]}$ | Low-power state                      |

<sup>[1]</sup> Active = HIGH; Inactive = LOW.

#### 4.2. Driver Interface Selection for ISP1104; ISP1105; ISP1106

Table 4-2: Driving Function

| Mode | VPO/VO | VMO/FSE0 | Data           | Interface           |

|------|--------|----------|----------------|---------------------|

| 0    | LOW    | LOW      | Differential 0 | Philips             |

|      | LOW    | HIGH     | SE0            | <b>Encoded Data</b> |

|      | HIGH   | LOW      | Differential 1 | Interface           |

|      | HIGH   | HIGH     | SE0            |                     |

| 1    | LOW    | LOW      | SE0            | USB-IF              |

|      | LOW    | HIGH     | Differential 0 | Standard Data       |

|      | HIGH   | LOW      | Differential 1 | Interface           |

|      | HIGH   | HIGH     | Illegal Data   |                     |

Table 4-3: Driving Function using the Single-Ended Input Data Interface ( $\overline{OE} = LOW$ ) [for ISP1104 and ISP1105 (MODE = LOW)]

|      | - /3 |                      |  |

|------|------|----------------------|--|

| FSE0 | VO   | DATA                 |  |

| LOW  | LOW  | Differential logic 0 |  |

| LOW  | HIGH | Differential logic 1 |  |

| HIGH | LOW  | SE0                  |  |

| HIGH | HIGH | SE0                  |  |

<sup>[2]</sup> In the suspend mode (SUSPND = HIGH), the differential receiver is inactive and output RCV is always LOW. Out-of-suspend ('K') signaling is detected through the single-ended receivers VP and VM.

<sup>[3]</sup> During suspend, the slew-rate control circuit of the low-speed operation is disabled. The D+ and D- lines are still driven to their intended states, without the slew-rate control. This is permitted because driving during suspend is used to signal remote wake-up by driving a 'K' signal (one transition from idle to the 'K' state) for a period of 1 ms to 15 ms.

<sup>[4]</sup> Signal levels on D+ and D- are determined using other USB devices and external pull-up and pull-down resistors.

Table 4-4: Driving Function using the Differential Input Data Interface ( $\overline{OE} = LOW$ ) [for ISP1104, ISP1105 and ISP1106 (MODE = HIGH)]

| , , , , , , , , , , , , , , , , , , , , |      |      |                      |

|-----------------------------------------|------|------|----------------------|

|                                         | VMO  | VPO  | DATA                 |

|                                         | LOW  | LOW  | SE0                  |

|                                         | LOW  | HIGH | Differential logic 1 |

|                                         | HIGH | LOW  | Differential logic 0 |

|                                         | HIGH | HIGH | Illegal state        |

#### Table 4-5: Receiving Function ( $\overline{OE} = HIGH$ )

| D+ and D-            | RCV     | $VP^{^{[1]}}$ | <b>VM</b> <sup>[1]</sup> |

|----------------------|---------|---------------|--------------------------|

| Differential logic 0 | LOW     | LOW           | HIGH                     |

| Differential logic 1 | HIGH    | HIGH          | LOW                      |

| SE0                  | RCV*[2] | LOW           | LOW                      |

<sup>[1]</sup> VP = VM = 'HIGH' indicates the sharing mode ( $V_{CC(5,0)}$  is disconnected).

#### 4.3. Driver Interface Selection for the ISP1102

Table 4-6: Driving Function using the Differential Input Data Interface ( $\overline{OE}$  = LOW)

[for ISP1102 Transmitting Function]

| <u>,                                      </u> |        |                      |  |

|------------------------------------------------|--------|----------------------|--|

| VM/VMO                                         | VP/VPO | DATA                 |  |

| LOW                                            | LOW    | SE0                  |  |

| LOW                                            | HIGH   | Differential logic 1 |  |

| HIGH                                           | LOW    | Differential logic 0 |  |

| HIGH                                           | HIGH   | Illegal state        |  |

Table 4-7: Driving Function using the Differential Input Data Interface ( $\overline{OE}$  = HIGH) [for ISP1102 Receiving Function]

| VM/VMO | VP/VPO | DATA                 |

|--------|--------|----------------------|

| LOW    | LOW    | SE0                  |

| LOW    | HIGH   | Differential logic 1 |

| HIGH   | LOW    | Differential logic 0 |

| HIGH   | HIGH   | Illegal state        |

|        |        |                      |

Table 4-8: Receiving Function ( $\overline{OE}$  = HIGH)

| (D+, D-)             | RCV                 | VP <sup>[1]</sup> | <i>VM</i> <sup>[1]</sup> |

|----------------------|---------------------|-------------------|--------------------------|

| Differential logic 0 | LOW                 | LOW               | HIGH                     |

| Differential logic 1 | HIGH                | HIGH              | LOW                      |

| SE0                  | $RCV^{\star^{[2]}}$ | LOW               | LIGH                     |

<sup>[1]</sup> VP/VPO = 'HIGH' and VM/VMO = 'HIGH' indicate the sharing mode ( $V_{CC(5.0)}$  is disconnected).

<sup>[2]</sup> RCV\* denotes the signal level on output RCV just before the SE0 state occurs. This level is kept stable during the SE0 period.

<sup>[2]</sup> RCV\* denotes the signal level on output RCV just before the SE0 state occurs. This level is kept stable during the SE0 period.

#### 5. Schematic of the ISP110x HVQFN14 and HVQFN16 Packages

Depending on the application, Table 5-1 and Table 5-2 provide guidelines for setting up the ISP110x HVQFN14 and HVQFN16 packages, respectively.

Table 5-1: Setting up the ISP110x HVQFN14 Package (U1A/B)

| Pin No | Pin Name | ISP1102 |

|--------|----------|---------|

| 1      | #OE      | #OE     |

| 2      | RCV      | RCV     |

| 3      | VP/VPO   | VP/VPO  |

| 4      | VM/VMO   | VM/VMO  |

| 5      | SUSPND   | SUSPND  |

| 7      | VBUSDET  | VBUSDET |

| 14     | SOFTCON  | SOFTCON |

Table 5-2: Setting up the ISP110x HVQFN16 Package (U2A/B)

| Pin No | ISP1102                | ISP1104                | ISP1105                | ISP1106            |

|--------|------------------------|------------------------|------------------------|--------------------|

| 6      | No connection          | MODE: Differential:    | MODE: Differential:    | MODE: JP13 and     |

|        |                        | when JP13 is used      | when JP13 is used      | JP12               |

|        |                        | Single-ended: when     | Single-ended: when     |                    |

|        |                        | JP12 and JP13 are used | JP12 and JP13 are used |                    |

| 8      | Not applicable         | Not applicable         | SPEED: full-speed;     | SPEED: full-       |

|        |                        |                        | low-speed (when JP7    | speed; low-speed   |

|        |                        |                        | is used)               | (when JP7 is used) |

|        | VBUSDET <sup>[1]</sup> | VBUSDET <sup>[1]</sup> | Not applicable         | Not applicable     |

| 4      | VM/VMO                 | VM                     | VM                     | VM                 |

| 3      | VP/VPO                 | VP                     | VP                     | VP                 |

| 11     | No connection          | VPO/VO                 | VPO/VO                 | VPO                |

| 12     | No connection          | VMO/FSE0               | VMO/FSE0               | VMO                |

<sup>[1]</sup> The VBUSDET pin is a  $V_{BUS}$  output indicator. When  $V_{BUS}$  is greater than 4.1 V, output is HIGH. When  $V_{BUS}$  is lower than 3.6 V, output is LOW. This feature is only applicable to the ISP1104.

#### 6. Bill of Materials for the ISP110x Eval Board

Table 6-1: Bill of Materials

| Description             | Reference                              | Value          | Quantity |

|-------------------------|----------------------------------------|----------------|----------|

| Power supply plugs      | PWR_Con1, PWR_Con2, PWR_Con3, PWR_Con4 | CON            | 4        |

| Tantalum capacitors     | C14, C15, C16                          | 18 pF          | 3        |

| Electrolytic capacitor  | C4                                     | 10 F           | 1        |

| Electrolytic capacitor  | C3                                     | 4.7 F          | 1        |

| Electrolytic capacitors | C1, C2                                 | 47 F           | 2        |

| Electrolytic capacitor  | C7, C20, C21, C22, C23                 | 1 F            | 5        |

| Tantalum capacitors     | C5, C6                                 | 33 pF          | 2        |

| Tantalum capacitors     | C10, C11                               | 150 pF         | 2        |

| Tantalum capacitors     | C8, C9                                 | 47 pF          | 2        |

| Tantalum capacitors     | C12, C13                               | 560 pF         | 2        |

| Probes                  | TP1, TP2                               | _              | 2        |

| Test Pin                | GP1, GP2, GP3, GP4, GP5, GP6, GP7      | -              | 7        |

| Header                  | JP7                                    | 7 X 2          | 1        |

| Header                  | JP12                                   | 3 X 2          | 1        |

| Header                  | JP3, JP4                               | 3 X 2          | 2        |

| Header                  | JP1, JP2, JP5, JP6                     | 2 X 2          | 4        |

| Jumpers                 | JP8, JP9, JP10, JP11, JP13, JP14, JP15 | _              | 7        |

| Resistors               | R5 to R9, R16 to R18                   | 1 ΜΩ           | 10       |

| Resistors               | R11, R12                               | 1.5 k <b>Ω</b> | 2        |

| Resistors               | R13, R14                               | 15 k <b>Ω</b>  | 2        |

| Resistors               | R1, R2                                 | 33 Ω           | 2        |

| Resistors               | R15                                    | 56 k <b>Ω</b>  | 1        |

| Ferrite bead            | Ferrite_bead1 (at 135MHz)              | _              | 1        |

| UP_CONN                 | CON1 (B Type)                          | _              | 1        |

| MOSFET P (ZVN2106)      | Q1                                     |                | 1        |

| ISP110x_HVQFN14         | U1B                                    | _              | 1        |

| ISP110x_HVQFN14_Socket  | U1A                                    |                | 1        |

| ISP110x_HVQFN16         | U2B                                    |                | 1        |

| ISP110x_HVQFN16_Socket  | U2A                                    | _              | 1        |

#### 7. References

- Universal Serial Bus Specification Rev. 2.0

- ISP1102 Advanced Universal Serial Bus transceiver data sheet

- ISP1104 Advanced Universal Serial Bus transceiver data sheet

- ISP1105\_1106 Advanced Universal Serial Bus transceivers data sheet.